Authors

Pablo Barrio, Carlos Carreras, Juan A. López, Óscar Robles, Ruzica Jevtic, Roberto Sierra

Journal Paper

http://doi.org/10.1016/j.sysarc.2014.07.001

Publisher URL

https://www.sciencedirect.com/

Publication date

August 2014

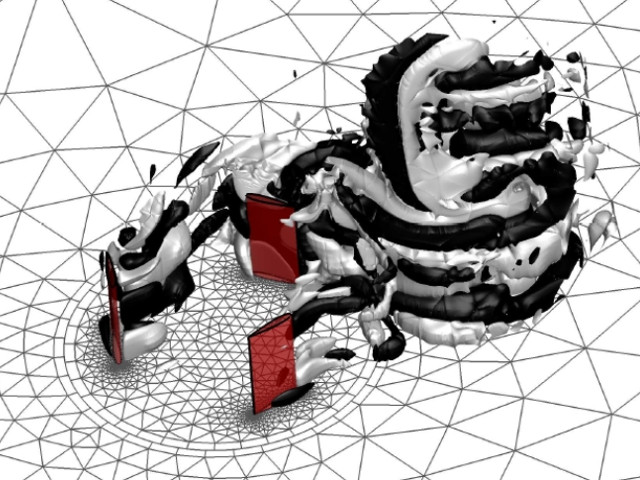

This paper approaches the memory bottleneck problem in FPGA-accelerated codes processing unstructured meshes. A methodology to reduce the required memory bandwidth is presented and evaluated, based on the combined application of data sorting, coding and compression techniques. Sorting allows efficient streaming between the memory and the FPGA, improving data locality and avoiding redundant data requests. Coding achieves a compact representation of the mesh connectivity. Differential compression reduces the size of the mesh data. We propose a hardware implementation with low resource requirements, tailored to accelerators based on reconfigurable devices. The combination of techniques reduces the memory traffic of two computational problems down to an average 34% and 19% of their original sizes, respectively.