Authors

Ranjita Kumari Dash ; Jose L. Risco-Martin ; Ashok Kumar Turuk ; Jose L. Ayala

Conference Paper

https://doi.org/10.1109/BIOSMART.2016.7835601

Publisher URL

Publication date

January 2017

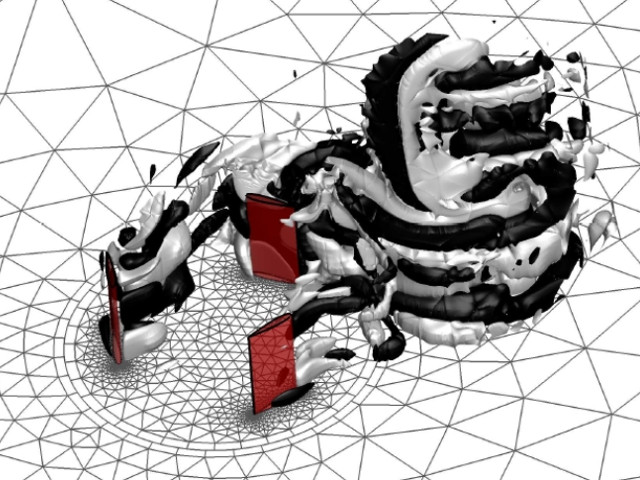

With 3D NoCs help improve circuit performance, fault tolerance and energy efficiency through the reduction of average wire-length and the increase in communication bandwidth of on-chip wiring, the soaring increase of on-chip temperature remains one of the most challenging obstacles to their commercialization. We present a physical design flow that integrates thermal driven floor-planning with MOEA. The thermal aware floor-planning help reduce the magnitude of hotspots in each layer, in turn, alleviate the negative impact of heat dissipation on chip performance and reliability. The essence of the flow is to analyze the layered thermal map of the chip stack and then apply MOEA operators, which helps to put the power hungry functional units far from each other. 3D stacked heterogeneous mesh architecture with 3 layers is used as the baseline for our experimental work. Further another two layers has been added to check the impact of increasing number of layers on the peak temperature of individual layers. The experimental results show the suitability of our algorithm for significantly reducing maximum on-chip temperature. As our approach is independent of any topology, it paves the way for thermal driven design methods consisting of 3D layouts made up of several layers.